DESIGNS” của các tác giả “CHRIS KWOK, PRIYA VISWANATHAN AND KURT TAKARA” và tổng hợp kiến thức bản thân.

Đây là bài báo khoa học mới nhất từ mentor graphic và mình đọc thấy rât là hay hi vọng bạn cũng học được từ nó.

Mình sẽ còn update phần hướng dẫn verify cho reset.

Tổng hợp, biên dịch, bổ sung và soạn thảo: TrongTran.

I. GIỚI THIỆU

Ngày nay, các thiết kế trong 1 hệ thống SoC có thể tích hợp từ nhiều khối IP được thiết kế từ nhiều nhà cung cấp khác nhau, mỗi nhà cung cấp lại có cách thiết lập reset cho IP riêng.

Trước đây, mô phỏng là phương pháp chính được sử dụng để verify cho hệ thống reset, thường phụ thuộc nhiều vào mô phỏng mức cổng. Tuy nhiên, các thử nghiệm mô phỏng cấp RTL thường không đầy đủ và mô phỏng cấp độ cổng chỉ có thể được chạy tại các phase khá muộn trong flow thiết kế. Thậm chí tệ hơn nữa là các lỗi liên quan đến reset thường có tính chất rất nghiêm trọng, khiến chip hoàn toàn không sử dụng được.

II. NHỮNG VẤN ĐỀ CHUNG

Trước tiên, mình nhấn mạnh một số vấn đề về reset phổ biến dựa vào kinh nghiệm thực tế của bản thân.

Mình sẽ tách nó thành hai loại chính:

Nhóm thứ hai của các vấn đề về reset có liên quan đến việc sử dụng tín hiệu reset để khởi động thiết kế.

Để mô tả tập hợp các vấn đề này, trước tiên chúng ta cần xác định các thuật ngữ có tên là reset domain và clock domain. Reset domain được đặc trưng bởi các thuộc tính sau:

Nhóm thứ ba của các vấn đề reset có liên quan đến các đường dẫn đặt lại tên miền (RDC) reset. Trường hợp đơn giản nhất của RDC là khi flip flop truyền và nhận được đặt tại các tín hiệu thuộc các miền reset khác nhau.

Trong bài viết này, mình đã trình bày một số vấn đề phổ biến về reset, các khó khăn khi verify và đề xuất một giải pháp toàn diện để giải quyết những thách thức này. Mình cũng đã chứng minh tính hiệu quả của giải pháp thông qua việc xác minh một số thiết kế của khách hàng và trình bày các vấn đề đã phát hiện được. Mình cũng chỉ ra nhiều vấn đề trong số này rất khó để phát hiện bằng các kỹ thuật mô phỏng hoặc xác minh truyền thống.

Tổng hợp, biên dịch, bổ sung và soạn thảo: TrongTran.

I. GIỚI THIỆU

Ngày nay, các thiết kế trong 1 hệ thống SoC có thể tích hợp từ nhiều khối IP được thiết kế từ nhiều nhà cung cấp khác nhau, mỗi nhà cung cấp lại có cách thiết lập reset cho IP riêng.

Kiến trúc reset của hệ thống cũng có thể trở nên rất phức tạp.

Một hệ thống SoC có thể có nhiều nguồn reset, chẳng hạn như:

- Power-on reset

- Hardware reset

- Debug reset

- Software reset

- Reset theo dõi bộ đếm thời gian

Các lỗi trong quá trình design liên quan đến reset có thể dẫn đến hiện tượng mestabilities, trục trặc hoặc các lỗi chức năng khác của hệ thống. Hơn nữa, các tương tác phức tạp có thể xảy ra với sự hội tụ của nhiều reset, nhiều clock và nhiều domain.

Trong nhiều trường hợp, điều này dẫn đến cây reset (reset tree) lớn hơn và phức tạp hơn cây clock (clock tree). Nhiều mối lo ngại liên quan đến việc tổng hợp và cân bằng tải của clock tree hiện cũng áp dụng cho reset tree. Rõ ràng, đó là một thách thức để đảm bảo rằng tất cả các nguồn reset truyền một cách an toàn đến các điểm đến mong muốn trong mọi điều kiện.

Trước đây, mô phỏng là phương pháp chính được sử dụng để verify cho hệ thống reset, thường phụ thuộc nhiều vào mô phỏng mức cổng. Tuy nhiên, các thử nghiệm mô phỏng cấp RTL thường không đầy đủ và mô phỏng cấp độ cổng chỉ có thể được chạy tại các phase khá muộn trong flow thiết kế. Thậm chí tệ hơn nữa là các lỗi liên quan đến reset thường có tính chất rất nghiêm trọng, khiến chip hoàn toàn không sử dụng được.

Nghiêm trọng hơn, thiết kế có thể tiêu thụ quá nhiều năng lượng trong quá trình xác nhận reset, khiến thiết bị quá nóng và bị hỏng vĩnh viễn. Tất cả các yếu tố này có thể khiến chúng ta phải thay đổi design tại các phase cuối gây tốn kém; và trong trường hợp xấu nhất, nó có thể gây thiệt hại nhiều triệu đô la và sự chậm trễ để tung sản phẩm ra thị trường.

II. NHỮNG VẤN ĐỀ CHUNG

Trước tiên, mình nhấn mạnh một số vấn đề về reset phổ biến dựa vào kinh nghiệm thực tế của bản thân.

Mình sẽ tách nó thành hai loại chính:

- Các vấn đề liên quan đến tính chính xác của cây reset (Reset tree).

- Các vấn đề liên quan đến việc sử dụng reset.

a.

Cây reset (Reset tree).

Đầu

tiên mình sẽ đề cập đến những

vấn đề liên quan đến việc triển

khai reset không chính xác. Những vấn đề này thường được phát hiện trong cây

reset (Reset tree).

Hình bên dưới cho thấy một ví dụ, nếu cây reset này không

chính xác, thì tất cả các kiểm tra khác có nguồn từ nó trong thiết kế cũng sẽ không chính xác và chip sẽ không hoạt động

đúng.

Trong

hình bên dưới nếu tín hiệu rst hoạt động không đúng thì 2 tín hiệu outputs là

rsta và rstb cũng hoạt động không đúng từ đó các mạch về sau cũng không thể verify chính xác được.

Nhìn chung, reset chỉ có thể được định nghĩa là:

Reset không đồng bộ với clock

Reset đồng bộ với

clock

Đôi khi, Một tín hiệu reset có thể vừa đồng bộ với clock1 và vừa bất đồng bộ với clock2. Điều này thường gây ra sự hiểu lầm về reset trong hệ thống. Hình

bên dưới cho thấy một sơ đồ đơn giản trong đó reset được sử dụng cả không đồng

bộ và đồng bộ.

Trong

hình trên khối A là khối reset đồng bộ với tín hiệu clock. Còn khối B là khối reset

bất đồng bộ với clock.

Ta

xét đơn giản:

Tại

khối B, Khi RST = 0, Ngay lập tức tín hiệu ngõ ra của Flip Flop trở về trạng

thái ban đầu bất chấp clock tại thời điểm đó là lên hay xuống.

Tại

khối A, Khi RST = 0, lúc đó bộ mux2to1 sẽ cho tín hiệu 1’b0 đi vào chân D của

Flip Flop và khi có clock cạnh lên thì Flip flop mới gửi tín hiệu từ chân D = 0

qua chân Q ra ngoài. Như vậy đó là reset đồng bộ.

Đôi khi trong quá

trình thiết kế, Logic sai có

thể được chèn vào cây reset. Logic không chính xác có thể đến trong các hình thức

khác nhau. Một số vấn đề phổ biến bao gồm việc bổ sung bộ đệm và cổng tristate

như cổng XOR, Hai hình bên dưới:

Việc triển khai phân phối reset

bao gồm reset nguồn, reset

hierarchy

và reset của

các phần tử logic, tất cả đều được

liệt

kê chi tiết trong cây reset được tạo

bởi các công cụ. Rà soát các chi tiết của thông tin cây reset có thể giải quyết

nhiều vấn đề về thiết

kế reset như mình phân tích bên trên.

b.

Sử dụng

reset.

Nhóm thứ hai của các vấn đề về reset có liên quan đến việc sử dụng tín hiệu reset để khởi động thiết kế.

Để mô tả tập hợp các vấn đề này, trước tiên chúng ta cần xác định các thuật ngữ có tên là reset domain và clock domain. Reset domain được đặc trưng bởi các thuộc tính sau:

a) Loại: Đồng bộ hoặc không đồng

bộ

b) Phân cực:

Hoạt động thấp hoặc hoạt động cao

c) Giá trị: Được set với 1 và reset với 0

d) Là tín hiệu reset trên cùng (Top

reset).

Nhiều tín hiệu

reset domain đồng bộ có thể

được nhóm lại với nhau. Tương tự, Nhiều nguồn

clock đồng bộ có thể được nhóm lại

trong một clock domain.

Khi reset chuyển từ trạng thái

đang reset sang trạng thái hoạt động (từ 0 -> 1). Tất cả tín hiệu

reset không đồng bộ phải được đồng bộ hóa với miền clock trước khi được sử dụng.

Nếu vi phạm có thể gây ra hiện tượng mestabilities.

Để bảo vệ mạch khỏi hiện tượng mestabilities do reset, cần phải chèn một

mạch đồng bộ reset 2 Flip Flop. Hai hình bên dưới hiển thị mạch đồng bộ

tín hiệu reset 2 FF điển hình. Mình sẽ giải thích ngắn gọn vấn

đề này như sau khi một thiết kế đang hoạt động bình thường.

Chúng ta sẽ có các hành động như sau:

Bước 1: Reset hệ thống nghĩa là

RST = 0 vài chu kì.

Bước 2: Bật lại hệ thống nghĩa

là RST = 1.

Tại bước 1 hệ thống có thể

reset bất đồng bộ (RST từ 1 -> 0). Điều này không ảnh hưởng gì quá trình hoạt

động.

Tuy nhiên, tại bước 2, khi muốn

chuyển từ trạng thái đang reset sang trạng thái hoạt động, tín hiệu reset cần

phải bậc đồng bộ với clock để tránh hiện tượng mestabilities như trình bày bên

trên.

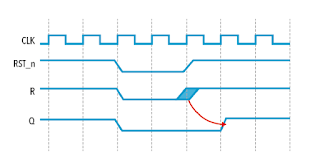

Hình sau cho thấy dạng

sóng ở đầu ra khi chèn mạch đồng bộ. Lưu ý rằng hiện tượng mestabilities không

còn xảy ra và việc khởi động hệ thống (Không reset nữa) bị hoãn bởi một

chu kỳ tại ngõ ra Q của Flip Flop thứ 2.

Vậy khi sau khi reset đi qua mạch

đồng bộ tín hiệu reset 2 Flip Flop ta tiếp tục phân tích tiếp 2 vấn đề phổ biến.Khi reset được

đồng bộ hóa, các nhà thiết kế phải đảm bảo rằng các tín hiệu reset được sử dụng

đúng cách trong các mạch phía sau. Hai vấn đề phổ biến cần được quan tâm

đó là:

- Reset được sử dụng với phân cực đúng cho các mạch phía sau

- Reset được sử dụng với clock đúng cho các mạch phía sau.

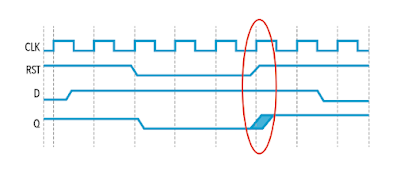

Hình bên dưới đã nêu ra 1 trường hợp sai trong việc sử dụng reset bất

đồng bộ với clock cho các mạch phía sau. Lỗi này có thể được phát hiện bởi việc

phân tích Clock-Domain Crossing (CDC).

Tiếp theo ta có 1 vấn đề khác đó là FF phía sau đang sử dụng reset tích cực

mức cao, trong khi mạch đồng bộ tín hiệu reset 2 Flip Flop phía trước là dành

cho reset tích cực mức thấp. Vì đây không phải là giao thoa CDC,

lỗi này sẽ không bị phát hiện bằng cách phân tích CDC và không thể bị phát hiện

dễ dàng.

c. Reset nhiều miền (RDC).

Nhóm thứ ba của các vấn đề reset có liên quan đến các đường dẫn đặt lại tên miền (RDC) reset. Trường hợp đơn giản nhất của RDC là khi flip flop truyền và nhận được đặt tại các tín hiệu thuộc các miền reset khác nhau.

Hình dưới cho thấy một đường dẫn RDC đơn giản. Nếu RST1 bị reset trong khi

RST2 không được reset, DFF2 có thể lấy mẫu dữ liệu bất đồng bộ. Điều kiện

để DFF2 lấy mẫu dữ liệu bất đồng bộ là nếu lúc tín hiệu reset của DFF1 bị reset

tại thời điểm trong setup time và hold time thì đầu ra

DFF2 sẽ bị hiện tựng mestabilities, như trong dưới.

III. PHẦN KẾT LUẬN

Trong bài viết này, mình đã trình bày một số vấn đề phổ biến về reset, các khó khăn khi verify và đề xuất một giải pháp toàn diện để giải quyết những thách thức này. Mình cũng đã chứng minh tính hiệu quả của giải pháp thông qua việc xác minh một số thiết kế của khách hàng và trình bày các vấn đề đã phát hiện được. Mình cũng chỉ ra nhiều vấn đề trong số này rất khó để phát hiện bằng các kỹ thuật mô phỏng hoặc xác minh truyền thống.

Cảm ơn mọi người đã đọc.

No comments:

Post a Comment