Biên dịch, tổng hợp và sắp xếp: Trần Văn Trọng.

Tài liệu tham khảo: Sách computer system design system-on-chip (Chương 4) và một số nguồn trên internet.

Đồng thời mình cũng gửi lời cảm ơn sâu sắc đến Thầy Nguyễn Lý Thiên Trường (Giảng viên ĐH Bách Khoa TP.HCM) đã hướng dẫn và giúp mình tìm hiểu về bài viết này.

I. Tổng quan.

Thiết kế memory là chìa khoá của thiết kế hệ thống. Hệ thống memory trên chip thường là phần đắt nhất và quyết định đến performance của hệ thống nhiều nhất.

Trong 1 hệ thống SoC có 3 yếu tố quyết định đến hiệu suất của hệ thống đó là:

- Memory

- Bộ xử lí (processors)

- Bus (interconnection) và IO.

Trong đó Memory đóng vai trò cực kì quan trọng và là thành phần quan trọng nhất trong việc quyết định performance của chip SoC.

Để thiết kế memory cho 1 chip cụ thể, ta cần cân nhắc các yếu tố sau:

- Hệ điều hành.

- Kích thước.

- Tính biến đổi của quy trình ứng dụng.

Điều này quyết định quan trọng đến kích thước của memory và cách thức thiết kế memory thực hay ảo.

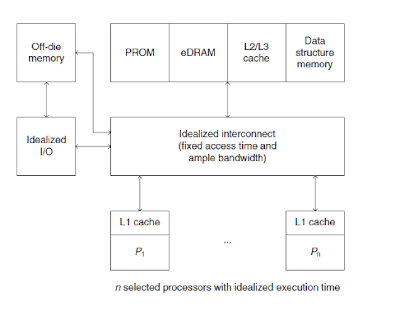

Hình 1.0 Các yếu tố ảnh hưởng đến performance của hệ thống

Chúng ta có sự đánh đổi (trade-off) giữa 3 yếu tố liên quan đến performance của một chip SoC:

- Vi xử lí (Processor)

- Interconnection và IO

- Memory

Trong bài này ta sẽ xem xét bộ xử lí và interconnection là lý tưởng để tập trung giải quyết và so sánh các vấn đề liên quan đến memory.

Hình 1.1 Lựa chọn memory cho chip SoC

Vị trí bộ nhớ

Yếu tố quan trọng và quyết định lớn nhất trong thiết kế hệ thống bộ nhớ là vị trí của bộ nhớ chính. Có hai vị trí mà bộ nhớ chính được đặt đó là on-die (cùng die với bộ vi xử lý) hoặc off-die (trên die dành cho memory hoặc trên một module có nhiều die mà không trùng với die của bộ xử lí).

Thiết kế của hệ thống bộ nhớ bị giới hạn bởi hai tham số cơ bản xác định hiệu năng của hệ thống bộ nhớ.

- Đầu tiên là thời gian truy cập (Access time). Đây là thời gian để bộ xử lý gửi một request đến hệ thống bộ nhớ, truy cập dữ liệu và trả dữ liệu lại cho bộ vi xử lý. Thời gian truy cập được quyết định bởi các tham số vật lý của hệ thống bộ nhớ - khoảng cách giữa bộ xử lý và hệ thống bộ nhớ, hoặc độ trễ bus, độ trễ chip, ..v..v.

- Tham số thứ hai là băng thông bộ nhớ (BW). Đó là khả năng của bộ nhớ để đáp ứng lại các request trên mỗi đơn vị thời gian. Băng thông chủ yếu được xác định theo cách tổ chức hệ thống bộ nhớ vật lý - số lượng mảng bộ nhớ độc lập và sử dụng các chế độ truy cập tuần tự đặc biệt. Hệ thống bộ đệm phải bù cho các giới hạn về thời gian truy cập bộ nhớ và băng thông.

Trong các ngành công nghệ hiện nay, Bộ xử lý máy trạm có hiệu năng cao, đòi hỏi một hệ thống bộ nhớ phải thật sự hiệu quả, Việc thiết kế bộ nhớ cho các hệ thống như vậy là thách thức đối với các nhà thiết kế hiện nay.

Kích thước của bộ nhớ.

Thiết kế cho bộ nhớ lớn là vấn đề chính trong thiết kế hệ thống SoC. Vậy tại sao không giới hạn bộ nhớ ở các kích thước có thể được kết hợp trên một die ? Trong một hệ thống bộ nhớ ảo, chúng ta vẫn có thể truy cập các không gian địa chỉ lớn cho các ứng dụng. Thế thì có bao nhiêu bộ nhớ chúng ta có thể đặt trên một die ? Điều đó phụ thuộc vào công nghệ (Tính năng kích thước) và hiệu suất cần thiết.

Bộ nhớ nhỏ hầu như luôn luôn nhanh hơn bộ nhớ lớn hơn, vì vậy rất hữu ích khi lưu trữ các tập lệnh và dữ liệu thường xuyên được sử dụng, giúp dễ truy cập (truy cập một chu kỳ). Nếu bộ nhớ này được lập trình viên quản lý trực tiếp, nó được gọi là bộ nhớ Scratchpad; nếu nó được quản lý bởi phần cứng, nó được gọi là bộ nhớ đệm.

Tính tuần tự.

Giả sử vi xử lí read/write đến một vị trí s, có thể trong một vài request tiếp theo, sẽ có một tham chiếu đến vị trí của s + 1. Đây là một trường hợp đặc biệt của local space.

Người thiết kế bộ đệm một mặt phải giải quyết các yêu cầu truy cập của bộ xử lý và mặt khác là các yêu cầu của hệ thống bộ nhớ. Thiết kế bộ đệm hiệu quả cần cân bằng những điều này để hạn chế chi phí.

II. Bộ nhớ ngoài SoC: flash.

Công nghệ Flash là một công nghệ phát triển nhanh với những cải tiến được công bố một cách thường xuyên. Flash không thể thay thế bộ nhớ trong một cách hoàn toàn nhưng có thể được xem như là một sự thay thế hoàn hảo cho đĩa. Bộ nhớ flash bao gồm một loạt các bóng bán dẫn cổng. Các bóng bán dẫn này tương tự như các bóng bán dẫn MOS nhưng có cấu trúc hai cổng: cổng điều khiển và cổng kết nối cách điện.

Hình 2.0 Cấu trúc một flash memory cell

Mặc dù có những ưu điểm rõ rệt. Tuy nhiên, Giới hạn về chu kỳ ghi dẫn đến việc hạn chế sử dụng bộ nhớ flash để lưu trữ cho các dữ liệu được truy cập thường xuyên, chẳng hạn như các tập lệnh của vi xử lí hoặc thanh ghi. Bộ nhớ flash thường được sử dụng nhằm mục đích chứa các chương trình và các tệp lớn. Có hai loại bộ nhớ flash là NOR và NAND tuỳ thuộc vào cấu trúc.

Trong bộ nhớ flash, mỗi cell trong bộ nhớ giống như một bóng bán dẫn hiệu ứng trường (MOSFET) ngoại trừ bóng bán dẫn có hai cổng thay vì một. Các cell có thể được xem như một công tắc điện trong đó dòng điện chạy giữa hai thiết bị đầu cuối (nguồn và cống) và được điều khiển bởi một cổng nổi (FG) và cổng điều khiển (CG). CG tương tự như cổng trong các bóng bán dẫn MOS khác, nhưng bên dưới này, có FG được cách điện xung quanh bởi một lớp oxit. FG được đặt xen kẽ giữa kênh CG và kênh MOSFET. Do FG bị cách ly bởi lớp cách điện của nó, các electron đặt trên nó bị giữ lại. Khi FG được tích điện bằng electron, điện tích này sẽ sàng lọc điện trường từ CG, do đó, làm tăng điện áp ngưỡng (VT1) của tế bào. Điều này có nghĩa là bây giờ điện áp cao hơn (VT2) phải được áp dụng cho CG để làm cho kênh dẫn. Để đọc giá trị từ bóng bán dẫn, một điện áp trung gian giữa các điện áp ngưỡng (VT1 & VT2) được áp dụng cho CG. Nếu kênh dẫn ở điện áp trung gian này, FG phải được tích điện (nếu được sạc, chúng tôi sẽ không được dẫn vì điện áp trung gian nhỏ hơn VT2), và do đó, "1" logic được lưu trữ trong cổng. Nếu kênh không dẫn ở điện áp trung gian, nó chỉ ra rằng FG được tích điện và do đó, "0" logic được lưu trữ trong cổng.

Hình 2.1 Cấu trúc NOR flash

Hình 2.2 Cấu trúc NAND flash

Thẻ nhớ flash có nhiều định dạng khác nhau; Cùng với sự phát triển của cộng nghệ các thẻ nhớ flash ngày càng có kích thước nhỏ và có dung lượng lớn hơn.

Hình 2.3 Bảng so sánh giữa NAND và NOR flash

III. Bộ nhớ cache.

Bộ nhớ cache là bộ nhớ truy cập nhanh một vùng đặc biệt của các chip nhớ tốc độ nhanh, được dành riêng để lưu giữ các thông tin thường xuyên được truy xuất từ RAM. Giống với bộ nhớ cache ngoài (external cache), Bộ nhớ cache thường là một đoạn nhỏ (32 K đến 512 K) của các chip RAM tĩnh tốc độ rất nhanh (SRAM) cùng với bus riêng của nó nối với đơn vị xử lý trung tâm ( CPU), và thường được dùng để lưu giữ dữ liệu và mã lệnh mà CPU hay truy cập đến.

Khi CPU yêu cầu dùng lại dữ liệu này, nó sẽ được cung cấp ngay theo đúng tốc độ hoạt động của bộ vi xử lý. Vì cache giao tiếp trực tiếp với CPU, nên bus có thể dùng bộ nhớ cache lớn để nâng cao hơn nữa hiệu suất của bộ nhớ. Bộ nhớ cache khác với cache phần mềm; đó là khu vực của bộ RAM bình thường, được dành riêng để lưu giữ những thông tin thường được lấy từ các ổ đĩa ra.

Chính sách ghi (Hay còn gọi là write policy)

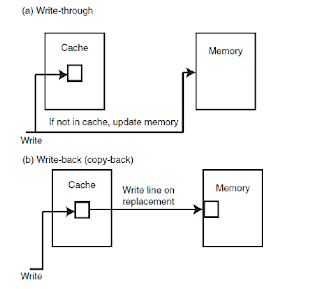

Làm thế nào để bộ nhớ được cập nhật ? Người ta có thể ghi vào cả bộ nhớ đệm và bộ nhớ chính (write-through hoặc WT) hoặc chỉ ghi vào bộ nhớ đệm (copy-back hoặc CB - đôi khi được gọi là write-back), cập nhật bộ nhớ khi thay thế dòng. Hai cách này là các cách ghi vào bộ nhớ đệm cơ bản.

- Bộ nhớ đệm với write-through lưu trữ dữ liệu vào cả bộ nhớ cache và bộ nhớ chính mỗi khi nhận request write từ CPU. Ưu điểm: Điều này tạo tính nhất quán hoạt động của chương trình trong bộ nhớ. Nhược điểm: Băng thông bộ nhớ có thể cao vì bị chi phối bởi lưu lượng ghi.

- Trong bộ nhớ đệm với copy-back, dữ liệu mới được ghi vào bộ nhớ chính chỉ khi dữ liệu tại đó được truy xuất từ lần thứ 2 trở đi. Điều này đòi hỏi cách thức để đánh dấu các dữ liệu đã được truy cập 1 lần trước đó (còn gọi là dirty).

Dưới đây là cơ chế ghi cho bộ đệm copy-back:

1. Đánh dấu dữ liệu tại một vị trí là dirty nếu nó được truy cập cho việc WRITE tại đó.

2. Khi CPU gửi request tiếp tục truy cập vào dữ liệu được đánh dấu dirty trước đó thì dữ liệu sẽ được ghi vào bộ nhớ chính phía sau bộ nhớ cache (Có thể là DRAM).

Hình 3.0 Cơ chế write cho bộ nhớ cache

Hầu hết các bộ nhớ cache lớn thường sử dụng copy-back; bộ nhớ với write-through thường được giới hạn trong các bộ nhớ nhỏ hoặc bộ nhớ chuyên dụng cung cấp hình ảnh cập nhật của bộ nhớ.

Hình 3.1 Cơ chế write-through

Hình 3.2 Cơ chế write-back

Cuối cùng, chúng ta nên làm gì khi một lệnh ghi (hoặc lưu trữ) bị mất trong bộ đệm? Chúng ta có thể tìm nạp dòng đó từ bộ nhớ (phân bổ ghi hoặc WA) hoặc chỉ ghi vào bộ nhớ (không phân bổ ghi hoặc NWA). Hầu hết các bộ đệm thông tin không phân bổ cho write (WTNWA) và hầu hết các bộ đệm sao chép lại phân bổ (CBWA).

Điều gì xảy ra trên một bộ nhớ cache miss rate? Nếu không tìm thấy dữ liệu tham chiếu trong thư mục, sẽ xảy ra lỗi bộ nhớ cache. Phải nhanh chóng thực hiện hai hành động:

- Dòng bị bỏ lỡ phải được lấy từ bộ nhớ chính

- Một trong các dòng bộ đệm hiện tại phải được chỉ định để thay thế bởi dòng hiện đang truy cập (dòng bị bỏ lỡ).

Thay thế dòng

Chính sách thay thế chọn một dòng để thay thế khi bộ đệm đầy. Có ba phương pháp thay thế được sử dụng rộng rãi:

1. Dữ liệu ít được sử dụng gần đây nhất(LRU) bằng cách đọc hoặc ghi sẽ được thay thế.

2. Đầu vào - Đầu ra (FIFO). Dòng đã ở trong bộ đệm lâu nhất được thay thế.

3. Thay thế ngẫu nhiên (RAND). Thay thế được xác định ngẫu nhiên.

Phương pháp LRU tương ứng với khái niệm về địa phương tạm thời, nên nhìn chung chính sách này được ưu tiên. Nó cũng là phức tạp nhất để thực hiện. Mỗi dòng có một bộ đếm, nó sẽ được cập nhật khi có bất kì một request đọc/ghi nào.

Mặc dù phương pháp LRU hoạt động tốt hơn cả FIFO hoặc RAND, nhưng việc sử dụng RAND hoặc FIFO đơn giản hơn chỉ khuếch đại tỷ lệ bỏ lỡ LRU (DTMR) khoảng 1,10 (tức là, 10%).

Giới hạn về kích thước bộ nhớ Cache

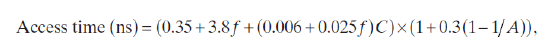

Cache bao gồm một mảng RAM tĩnh (SRAM) của các ô lưu trữ. Khi mảng tăng kích thước, đã làm tăng chiều dài của dây cần thiết để truy cập vào ô xa nhất của nó. Điều này chuyển thành độ trễ (Latency) truy cập bộ nhớ đệm. McFarland đã mô hình hóa độ trễ và thấy rằng một xấp xỉ có thể được biểu diễn dưới dạng thời gian truy cập:

Trong đó f là kích thước tính năng tính bằng micron, C là dung lượng mảng bộ nhớ cache tính bằng kilobyte và A là mức độ kết hợp (trong đó ánh xạ trực tiếp = 1).

Hiệu quả của phương trình này (cho A = 1) có thể được nhìn thấy. Nếu chúng ta giới hạn thời gian truy cập của bộ nhớ cache cấp 1 dưới 1 ns, có lẽ chúng ta bị giới hạn ở một mảng bộ nhớ đệm khoảng 32 KB (Hình trên). Trong khi đó ta có thể xen kẽ nhiều cấp bộ nhớ cache. Thời gian truy cập (Access time) cho cấp đầu tiên nhỏ hơn so với cấp thừ 2 và tiếp theo nữa. Thời gian truy cập lớn nhất là khi vi xử lí truy cập đến bộ nhớ chính.

Hình 3.3 Biểu đồ tương quan giữa kích thước bộ nhớ đệm và độ trễ.

Vì vậy, thông thường, bộ nhớ cache L1 nhỏ hơn 64 KB; Bộ nhớ cache L2 thường nhỏ hơn 512 KB (có thể được xen kẽ bằng cách sử dụng các mảng nhỏ hơn); và bộ đệm L3 sử dụng nhiều mảng từ 256 KB trở lên để tạo bộ đệm lớn, thường bị giới hạn bởi kích thước khuôn.

Đánh giá bộ nhớ cache đa cấp

Trong trường hợp bộ nhớ đệm đa cấp, chúng ta có thể đánh giá hiệu suất của cả hai (Hoặc 3) cấp bằng cách sử dụng dữ liệu bộ đệm L1. Một hệ thống bộ đệm hai cấp được gọi là including nếu tất cả nội dung của bộ đệm cấp thấp hơn (L1) được chứa trong bộ đệm cấp cao hơn (L2). Phân tích bộ đệm cấp hai được thực hiện bằng cách sử dụng nguyên tắc đưa vào; nghĩa là, bộ đệm lớn, cấp hai bao gồm các dòng giống như trong bộ đệm cấp thứ nhất. Do đó, với mục đích đánh giá hiệu năng, chúng ta có thể giả sử rằng bộ đệm cấp đầu tiên không tồn tại. Tổng số lỗi xảy ra trong bộ đệm cấp hai có thể được xác định bằng cách giả sử rằng bộ xử lý đã thực hiện tất cả các yêu cầu của nó tới bộ đệm cấp hai mà không có bộ đệm cấp thứ nhất. Có những cân nhắc về thiết kế trong việc cung cấp bộ đệm cấp hai cho bộ đệm cấp thứ nhất hiện có. Kích thước dòng của bộ đệm cấp hai phải bằng hoặc lớn hơn bộ đệm cấp thứ nhất. Mặt khác, nếu kích thước dòng trong bộ đệm cấp hai nhỏ hơn, việc tải dòng trong bộ đệm cấp thứ nhất sẽ chỉ gây ra hai lỗi trong bộ đệm cấp hai. Hơn nữa, bộ đệm cấp hai phải lớn hơn đáng kể so với cấp đầu tiên; nếu không, nó sẽ không có lợi ích.

Hình 3.4 Bộ nhớ cache 2 cấp L1 và L2

Trong một hệ thống hai cấp độ, như trong Hình 3.4, với bộ đệm cấp độ đầu tiên, L1 và bộ đệm cấp hai, L2, chúng ta định nghĩa các tỷ lệ bỏ lỡ như sau:

- Tỷ lệ bỏ lỡ cục bộ đơn giản là số lần bỏ lỡ do bộ đệm chia cho số lượng tham chiếu đến nó. Đây là cách hiểu thông thường về tỷ lệ bỏ lỡ (miss rate).

- Tỷ lệ bỏ lỡ toàn cầu là số lần bỏ lỡ L2 chia cho số lượng tham chiếu được thực hiện bởi bộ xử lý. Đây là biện pháp chính của chúng tôi về bộ đệm L2.

- Tỷ lệ bỏ lỡ solo là tỷ lệ bỏ lỡ bộ đệm L2 sẽ có nếu đó là bộ đệm duy nhất trong hệ thống. Đây là tỷ lệ bỏ lỡ được xác định theo nguyên tắc including. Nếu L2 chứa tất cả L1, thì chúng ta có thể tìm thấy số lần bỏ lỡ L2 và tốc độ tham chiếu của bộ xử lý, bỏ qua sự hiện diện của bộ đệm L1. Nguyên tắc bao gồm thông số cụ thể rằng tỷ lệ bỏ lỡ toàn cầu giống như tỷ lệ bỏ lỡ solo, cho phép chúng tôi sử dụng tỷ lệ bỏ lỡ solo để đánh giá một thiết kế.

Dưới đây là kết quả đo đạc được:

Nếu dữ liệu hit tại L1 thì ta không tốn thời gian truy cập do L1 nằm trong bộ xử lí. Thời gain truy cập cho đến bộ nhớ cache L1 phụ thuộc vào hệ thống bus đặc biệt giữa vi xử lí và cache.

Nếu dữ liệu bị miss tại L1, và hit tại L2 (Nghĩa là L2 tốn tại dữ liệu cần truy cập) Ta sẽ tốn 2 cycle cho việc truy cập dữ liệu.

Nếu dữ liệu bị miss tại cả L1 và L2 ta tốn 15 cycle để truy cập dữ liệu từ bộ nhớ chính. Điều này cho thấy rõ rệt hiệu quả của việc thiết kế bộ nhớ đệm với nhiều level.

Dữ liệu minh họa một số điểm nổi bật trong phân tích và thiết kế bộ đệm đa cấp:

- Miễn là bộ đệm L1 giống hoặc lớn hơn bộ đệm L2, phân tích theo nguyên tắc including cung cấp ước tính tốt về hành vi của bộ đệm L2.

- Khi bộ đệm L2 lớn hơn đáng kể so với bộ đệm L1, nó có thể được coi là độc lập với các tham số L1. Tỷ lệ bỏ lỡ của nó tương ứng với tỷ lệ bỏ lỡ solo.

Mô hình nhiều bộ xử lý và bộ nhớ.

Để phát triển một mô hình bộ nhớ hữu ích, chúng ta cần một mô hình của bộ xử lý. Để phân tích, chúng ta mô hình hóa một bộ xử lý như một nhóm gồm nhiều bộ xử lý đơn giản. Mỗi bộ xử lý đơn giản đưa ra một yêu cầu ngay khi yêu cầu trước đó được đưa ra. Trong mô hình này, chúng ta có thể thay đổi số lượng bộ xử lý và số lượng module bộ nhớ và duy trì trạng thái cân bằng yêu cầu/cung cấp dữ liệu địa chỉ. Để chuyển đổi mô hình bộ xử lý đơn thành nhiều bộ xử lý tương đương, nhà thiết kế phải xác định số lượng yêu cầu cho module bộ nhớ trên mỗi đơn vị thờ, T s = T c. Một bộ xử lý đơn giản thực hiện một yêu cầu duy nhất và chờ phản hồi từ bộ nhớ. Một bộ xử lý pipelined thực hiện nhiều yêu cầu cho các bộ đệm khác nhau trước khi chờ phản hồi bộ nhớ. Có một sự tương đương gần đúng giữa n bộ xử lý đơn giản, mỗi yêu cầu một lần mỗi Ts và một bộ xử lý pipeline tiến hành n yêu cầu mỗi Ts.

Chúng ta sử dụng hai biểu tượng để biểu thị băng thông có sẵn từ hệ thống bộ nhớ (băng thông đạt được):

- B. Số lượng request được đáp ứng mỗi Ts.

- Bw. Số lượng request được đáp ứng mỗi giây: Bw = B / Ts

Để chuyển đổi điều này sang các hệ thống bộ nhớ đệm nền, thời gian phục vụ, Ts, là thời gian mà hệ thống bộ nhớ bận quản lý lỗi bộ nhớ cache. Số lượng mô-đun bộ nhớ, m, là số lượng bộ nhớ cache tối đa mà hệ thống bộ nhớ có thể xử lý cùng một lúc và n là tổng số request trên mỗi Ts. Đây là tổng số lần bỏ lỡ dự kiến cho mỗi bộ xử lý trên mỗi Ts nhân với số lượng bộ xử lý gửi request.

Kết luận.

Kích thước bộ đệm phần lớn xác định hiệu suất bộ đệm (tỷ lệ bỏ lỡ hay còn gọi là miss rate). Bộ nhớ cache càng lớn, tỷ lệ bỏ lỡ càng thấp. Dữ liệu bộ nhớ cache phụ thuộc mạnh vào chương trình. Ngoài ra, dữ liệu thường được dựa trên các máy cũ hơn, trong đó bộ nhớ và kích thước chương trình được chia ngày càng nhỏ. Dữ liệu này cho thấy tỷ lệ bỏ lỡ thấp đối với bộ đệm kích thước tương đối nhỏ. Do đó, có xu hướng tỷ lệ bỏ lỡ đo được của một kích thước bộ đệm cụ thể sẽ tăng theo thời gian. Đây chỉ đơn giản là kết quả của các phép đo được thực hiện trên các chương trình có kích thước tăng dần. Cách đây một thời gian, Smith [224] đã phát triển một loạt các tỷ lệ bỏ lỡ mục tiêu thiết kế (DTMR) đại diện cho ước tính về những gì một nhà thiết kế có thể mong đợi từ bộ đệm (hướng dẫn và dữ liệu) tích hợp và đưa ra ý tưởng về tỷ lệ bỏ lỡ điển hình như là một hàm của bộ đệm và kích thước dòng. Đối với kích thước bộ đệm lớn hơn 1 MB, một quy tắc chung là nhân đôi kích thước bằng một nửa tỷ lệ bỏ lỡ. Quy tắc chung là ít hợp lệ trong các chương trình dựa trên giao dịch.

Bộ nhớ cache cung cấp cho bộ xử lý thời gian truy cập bộ nhớ nhanh hơn đáng kể so với thời gian truy cập bộ nhớ thông thường. Như vậy, bộ đệm là một thành phần quan trọng trong bộ xử lý hiện đại. Tỷ lệ miss rate bộ đệm được xác định chủ yếu bởi kích thước của bộ đệm, nhưng mọi ước tính về tỷ lệ miss rate cần phải xem xét tổ chức bộ đệm, hệ điều hành, môi trường trên hệ thống và ảnh hưởng của I/O file. Vì thời gian truy cập bộ đệm bị giới hạn bởi kích thước, bộ nhớ cache nhiều cấp là một tính năng phổ biến của các thiết kế bộ xử lý on-die. Thiết kế bộ nhớ on-dei có vẻ tương đối dễ quản lý, đặc biệt là với sự ra đời của eDRAM, nhưng thiết kế bộ nhớ off-die là một vấn đề đặc biệt khó khăn. Mục tiêu chính của các thiết kế đó là công suất (hoặc kích thước); tuy nhiên, dung lượng bộ nhớ lớn và giới hạn pin sẽ làm thời gian truy cập chậm. Ngay cả khi các die có thể truy cập nhanh, hệ thống trên cao, Việc truyền tín hiệu bus, kiểm tra lỗi và phân phối địa chỉ, sẽ làm tăng độ trễ đáng kể. Thật vậy, các độ trễ trên không này đã tăng lên tương ứng với việc giảm thời gian chu kỳ máy. Đối mặt với thời gian truy cập bộ nhớ hàng trăm chu kỳ, nhà thiết kế có thể cung cấp băng thông bộ nhớ đầy đủ để phù hợp với tốc độ yêu cầu của bộ xử lý chỉ bằng một bộ đệm đa cấp rất lớn.

Trong hệ thống bộ nhớ đệm, thời gian cần thiết để đọc hoặc ghi dữ liệu vật lý từ bộ nhớ cache RAM chỉ chiếm một phần thời gian cần thiết để thực hiện truy cập đọc hoặc ghi bộ đệm. Đặc biệt là trong một hệ thống đa bộ xử lý, cũng cần xác định bộ

đệm được cho là phải làm gì trên bất kỳ quyền truy cập nào. Xem xét, ví dụ: một bộ đệm kết hợp tập hợp là liên kết bốn chiều, được chia cho bốn ngân hàng bộ nhớ. Khi bộ xử lý thực hiện yêu cầu đọc, bộ điều khiển bộ đệm sẽ biết ngay rằng nếu dữ liệu trong bộ đệm đó phải đến từ một địa chỉ đã biết ở một trong bốn ngân hàng. Bộ điều khiển bộ đệm có thể ngay lập tức bắt đầu yêu cầu đọc cho cả bốn ngân hàng song song (không điều khiển kích hoạt đầu ra) trước khi xác định chip nào, nếu có, thực sự giữ dữ liệu. Ít nhất ba trong số các ngân hàng sẽ lấy dữ liệu vô dụng, nhưng lấy dữ liệu vô ích là vô hại (ngoài việc lãng phí một số điện). Điều quan trọng là vào thời điểm bộ điều khiển tìm ra ngân hàng nào (nếu có) giữ dữ liệu và điều khiển kích hoạt đầu ra, các bộ nhớ sẽ có thời gian để xử lý yêu cầu truy cập.

Tuy nhiên, với một yêu cầu ghi, bộ điều khiển bộ đệm thực sự không thể bắt đầu thực hiện thao tác bộ nhớ cho đến khi nó biết chip nào được cho là được ghi. Một đọc vô dụng là vô hại; người ta có thể nói "không bao giờ để tâm" một cách hiệu quả và loại bỏ dữ liệu tìm nạp sai. Một văn bản vô dụng, tuy nhiên, không thể được hoàn tác. Do đó, điều quan trọng là dữ liệu không được ghi cho đến sau khi bộ điều khiển đã tìm ra nơi ghi được cho là sẽ đi.

Nếu một người chỉ thực hiện ghi bộ nhớ, người ta có thể thực hiện chúng nhanh như đọc bằng cách sắp xếp quá trình. Trong chu kỳ n, bộ điều khiển sẽ tìm ra nơi mà bộ nhớ byte n sẽ đi, trong khi byte n-1 được ghi vào vị trí được tính trong chu kỳ trước. Tuy nhiên, rất ít tình huống liên quan đến việc ghi nhiều bộ nhớ liên tiếp mà không can thiệp vào việc đọc. Nếu ghi thực tế vào bộ nhớ xảy ra trên chu kỳ sau khi yêu cầu ghi và bộ xử lý muốn thực hiện đọc trong chu kỳ đó, thì việc đọc sẽ phải chờ.

Trong nhiều trường hợp, các bài viết bị trì hoãn thêm bởi thực tế là nhiều hệ thống không cho phép các byte bộ nhớ được ghi riêng lẻ. Một hệ thống có thể có một bus 64 bit giữa bộ nhớ cache và bộ nhớ chính và có thể yêu cầu bộ nhớ chính chỉ được ghi trong các đoạn 64 bit. Nếu mã muốn ghi một byte đơn, sẽ cần phải đọc 64 bit từ RAM, ghi một byte vào bộ đệm và sau đó sau đó ghi 64 bit trở lại RAM. Có thể bộ đệm có thể thực hiện ghi trong khi dữ liệu đang được tìm nạp từ RAM chính, và sau đó khi có sẵn dữ liệu RAM chính, chỉ sao chép 56 bit không được ghi từ bus

bộ nhớ chính vào bộ đệm, nhưng logic này thêm vào phức tạp. Trong nhiều trường hợp, đơn giản hơn là chỉ cần trì hoãn ghi cho đến khi dòng bộ đệm được đọc từ RAM.

Trong các hệ thống đa bộ xử lý, mọi thứ còn phức tạp hơn nữa bởi thực tế là hai bộ xử lý có thể đọc liên tục cùng một dòng bộ đệm mà không bị nhiễu, nhưng nếu một bộ xử lý ghi một dòng bộ đệm thì bộ xử lý khác không được phép sử dụng dòng bộ đệm đó cho đến đầu tiên bộ xử lý đã ghi nó vào RAM chính và bộ xử lý thứ hai đã đọc nó hoặc bộ xử lý thứ nhất thông qua một số phương tiện khác được cung cấp dữ liệu trong đó cho bộ xử lý thứ hai. Một chuỗi các hoạt động bao gồm toàn bộ các lần đọc sẽ thực hiện nhanh hơn nhiều so với một chuỗi các hoạt động bao gồm một hỗn hợp giữa đọc và ghi (lưu ý rằng, trong nhiều trường hợp, các hoạt động dường như đòi hỏi chỉ thực sự sẽ bao gồm cả đọc và ghi ). Vấn đề không phải là quá nhiều đến nỗi bản thân ghi chậm hơn, mà là việc ghi trên một CPU có trước hoặc sau bất kỳ hoạt động nào của CPU khác sẽ yêu cầu cả hai CPU thực hiện bắt tay thêm, điều này không cần thiết nếu cả hai CPU chỉ đọc .

DRAM chậm ghi hơn đọc vì cần có thời gian để sạc hoặc xả một ô nhớ DRAM. Nhưng còn SRAM trong bộ nhớ cache L1 và L2 của bộ xử lý của tôi thì sao? Nó cũng chậm hơn để viết nhưng AFAIK, SRAM là bộ nhớ chốt dựa trên các cổng.

IV. Một số loại bộ nhớ khác.

DRAM là viết tắt của Dynamic random-access memory (Bộ nhớ truy cập ngẫu nhiên động hay RAM động), một loại bộ nhớ được sử dụng rộng rãi trên các hệ thống máy tính như là bộ nhớ chính. Xét về công suất, nó có thể đạt được 8GB cho mỗi chip trong IC hiện đại. Về mặt vật lý, DRAM lưu trữ mỗi bit dữ liệu trong một tụ điện riêng bên trong mạch tích hợp. Tụ điện có thể được nạp hoặc xả, hai trạng thái này đại diện cho hai trạng thái của một bit (thường được gọi là 0 và 1). DRAM được gọi là động vì nó cần được làm tươi (refresh) hoặc nạp điện sau khoảng vài mili giây để bù đắp cho sự rò rỉ điện từ tụ điện. Vì tụ điện bị rò điện nên nếu không được làm tươi hoặc nạp điện lại đều đặn thì các bit dữ liệu lưu trên DRAM sẽ mất dần. RAM truyền thống trên máy tính đều là DRAM. Những máy tính mới hơn sử dụng DDR (Dual Data Rate - tạm dịch: tốc độ dữ liệu kép) DRAM để nâng cao hiệu suất.

SRAM là viết tắt của Static random-access memory (Bộ nhớ truy cập ngẫu nhiên tĩnh hay RAM tĩnh). SRAM lưu giữ các bit dữ liệu trong bộ nhớ miễn là nguồn điện được cung cấp đầy đủ. Không giống như DRAM, lưu bit dữ liệu trong các pin chứa tụ điện và bóng bán dẫn, SRAM không cần phải làm tươi theo định kỳ. SRAM chỉ chứa bóng bán dẫn và biến tần, dữ liệu được đưa vào SRAM với sự trợ giúp của bitline và được chuyển tiếp bởi wordline. Biến tần được sử dụng để tạo feedback, dùng làm đầu vào cho các bóng bán dẫn, nhờ đó SRAM không cần phải làm mới hàng nghìn lần trong một chu kỳ như DRAM. Nhưng trong một bit bộ nhớ có 6 bóng bán dẫn của SRAM khiến cho nó khá cồng kềnh và đòi hỏi nhiều không gian hơn DRAM (1 bit bộ nhớ chỉ có 1 bóng bán dẫn của DRAM). Điện năng mà SRAM cần cũng nhiều hơn DRAM vì nó cần vận hành 6 bóng bán dẫn (thay vì 1 bóng như DRAM). SRAM nhanh hơn và đắt hơn DRAM, nó thường được sử dụng bên trong CPU. Do tốc độ cao, SRAM cũng được sử dụng như bộ nhớ cache và bộ nhớ chính trong các máy chủ để có hiệu năng tốt nhất. SDRAM là viết tắt của Synchronous dynamic random access memory (Bộ nhớ truy cập ngẫu nhiên động đồng bộ). SDRAM là DRAM được đồng bộ hóa với bus hệ thống. Đây là tên chung cho những loại DRAM khác nhau được đồng bộ hóa với tốc độ xung nhịp tối ưu của vi xử lý. SDRAM có thể chạy ở tốc độ xung nhịp cao hơn nhiều so với bộ nhớ thông thường. Được đồng bộ với bus của CPU và có khả năng chạy ở mức 133MHz, nhanh hơn khoảng 3 lần so với RAM FPM thông thường, nhanh hơn DRAM EDO và DRAM BEDO khoảng 2 lần. SDRAM đang dần thay thế DRAM EDO trong nhiều máy tính đời mới.

Bảng so sánh DRAM và SRAM

Trên đây là những gì mình tìm hiểu được về hệ thống memory trên chip SoC. Nếu bài viết có gì sai sót hoặc bạn muốn bổ sung phần nào vui lòng comment hoặc gửi mail về địa chỉ : trongk10@gmail.com. Cảm ơn ạ.

Thank

ReplyDelete